電路設計專欄 — Buck Part4 電路穩定補償

【請點我參閱 Buck Part1 電路專有名詞】【請點我參閱 Buck Part2 電路零件功能】【請點我參閱 Buck Part3 電路印刷電路板設計】

學習電路穩定補償的邏輯順序如下:

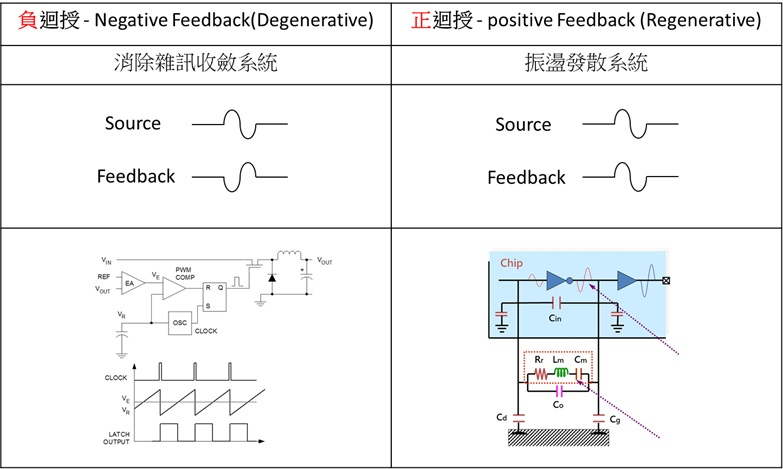

- 「負迴授」、「正迴授」的差異

- 頻率響應波德圖

- 穩定的條件

- 迴授控制模式類別

- 「開迴路」、「閉迴路」轉換方程式與頻率響應圖

- 補償電路類別

- 補償電路設計順序

- 電路驗證

下列以圖示的方法,介紹學習重點

「負迴授」、「正迴授」的差異

正迴授:振盪發散系統,例如Clock (時脈)。

負迴授:收斂穩定系統,例如DC/DC 迴授穩定輸出電壓,電路穩定補償期望操作在「負迴授」。

「正迴授」 vs 「負迴授」的比較表

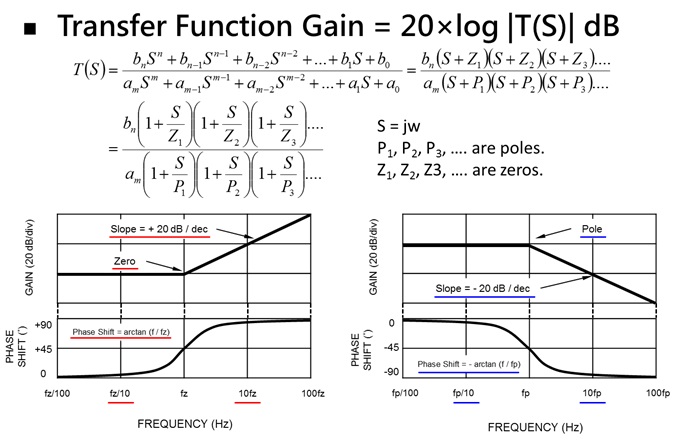

頻率響應波德圖

此處學習的重點在

- 透過轉換函數找出零點(Zero)與極點(Pole)

- 零點與極點對於增益(Gain)及相位(Phase)的貢獻。

例如Buck電壓控制模式(Voltage Control Mode)的輸出濾波器 (Output Filter),其中輸出電感與電容會貢獻兩個極點(Double Pole)、輸出電容的ESR會貢獻一個零點。

轉換函數 – 零點與極點

零點與極點比較表

| 轉換函數 | 增益 (Gain) | 相位 (Phase) | |

| 零點 (Zero) | 分子項 | + 20dB斜率上升(+1斜率) 影響範圍不會終止 |

相位抬升90° 影響範圍 1/10 * FZero ~ 10 * FZero |

| 極點 (Pole) | 分母項 | – 20dB斜率下降(-1斜率) 影響範圍不會終止 |

相位下降90° 影響範圍 1/10 * FPole ~ 10 * FPole |

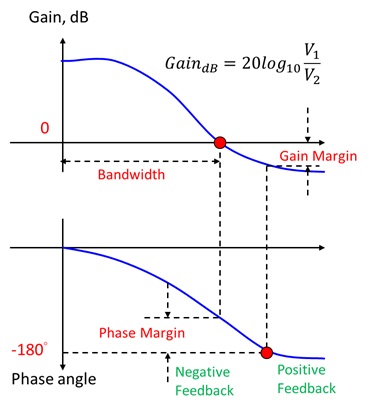

穩定的條件

此處學習的重點在

- 了解相位邊限(Phase Margin, P.M.)、增益邊限(Gain Margin, G.M.)、頻寬(Bandwidth, BW)的定義,及各項參數對於電路的影響,並規範不同電路下的穩定條件。例如較寬頻寬相對對於負載轉態反應速度較快。

| 定義 | 期望 | 影響 | |

| 相位邊限 (P.M.) Phase Margin |

Gain切 0 dB Phase離-180°還有幾度 |

Buck P.M. ≧ 45° LDO P.M. ≧ 30° |

穩定度 是否振盪 |

| 增益邊限 (G.M.) Gain Margin |

Phase切 -180° Gain負多少dB的絕對值 |

|G.M.| ≧ 6 dB | 高頻雜訊干擾 |

| 迴授頻寬 (BW) Bandwidth |

Gain切 0 dB的頻率點 | 20%FSW≦BW≦30%FSW | 寬:負載轉態反應速度快 窄:較容易穩定 |

另外在負迴授頻寬內的Gain,也會影響負載轉態的反應速度。

相位邊限、增益邊限、頻寬

而補償(Compensation)電路就是要「拉寬BW(反應速度 vs 穩定度)、增加P.M.(穩定)、增加G.M.(抑制高頻不要雜訊)」。注意此處的Phase(相位)談的是電路穩定議題,而Single Phase or Multi-phase是因應負載大小決定幾個Phase,一般期望一個Phase 負載上限為25A。

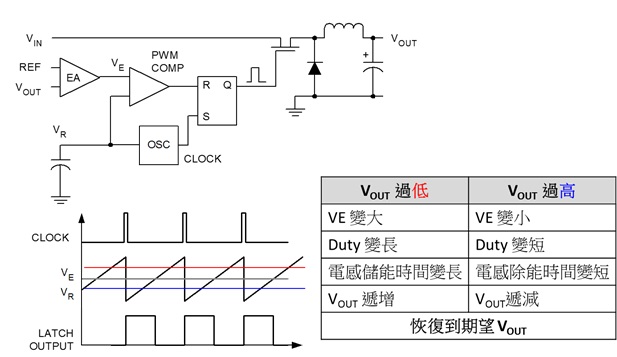

迴授控制模式類別

此處學習的重點在

- 了解電「壓控制模式、峰值or平均電流控制模式、COT控制模式」的動作原理及優缺點,搭配「輸出電容串聯等效阻抗、補償模式」管理電路穩定、反應速度、成本關係。

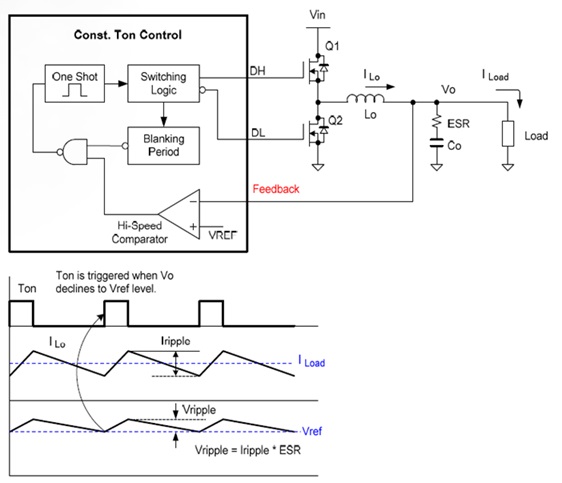

電壓控制模式

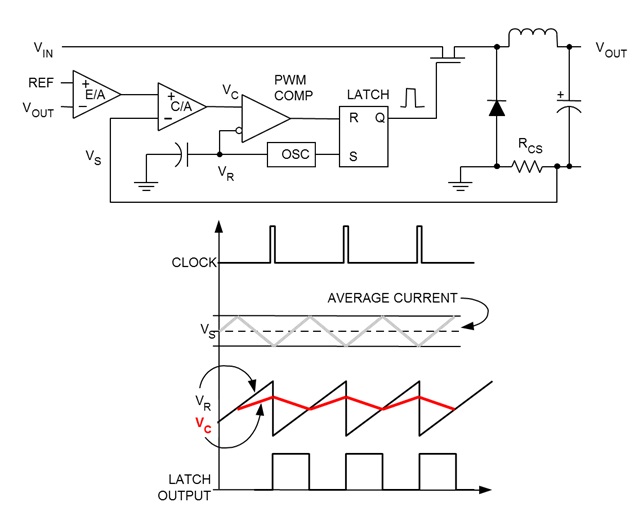

平均電流控制模式

峰值電流控制模式

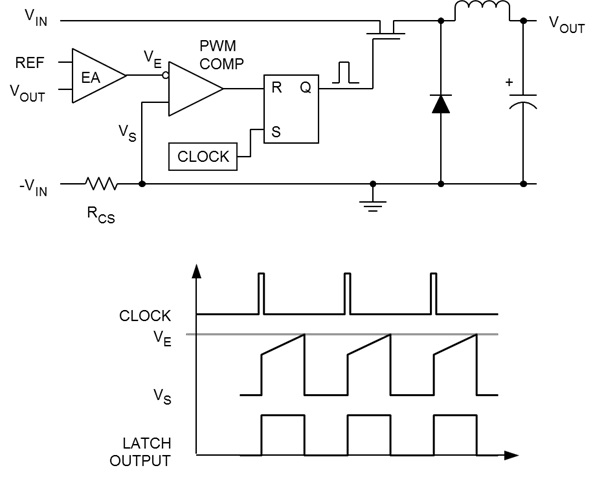

在Peak Current Mode 當Duty > 50%會造成不穩定,衍生另一個專有名詞斜率補償(Slop Compensation)。斜率補償的標的物是Duty,後續介紹Type 2 or 3的穩定補償(Compensation)的標的物為相位邊限、增益邊限、頻寬。

斜率補償

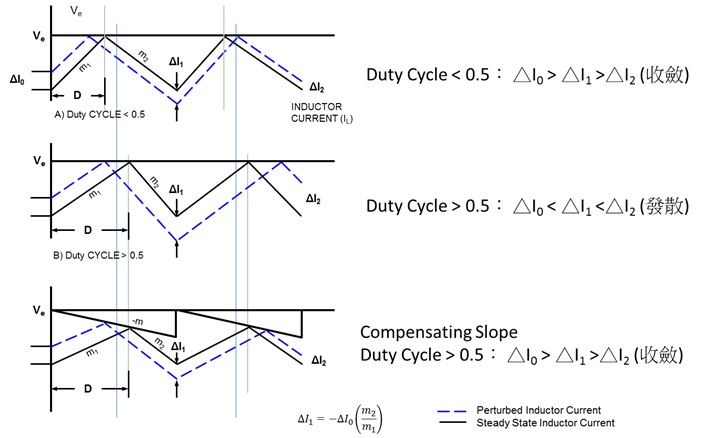

COT 控制模式

COT模式沒有Zero & Pole觀念,所以不需要進行波德圖量測,但有Min VOUT,RIPPLE的限制。

「開迴路」、「閉迴路」轉換方程式與頻率響應圖

此處學習的重點在

- 閉迴路的動作模式及頻率響應

- 個別方塊開迴路的頻率響應

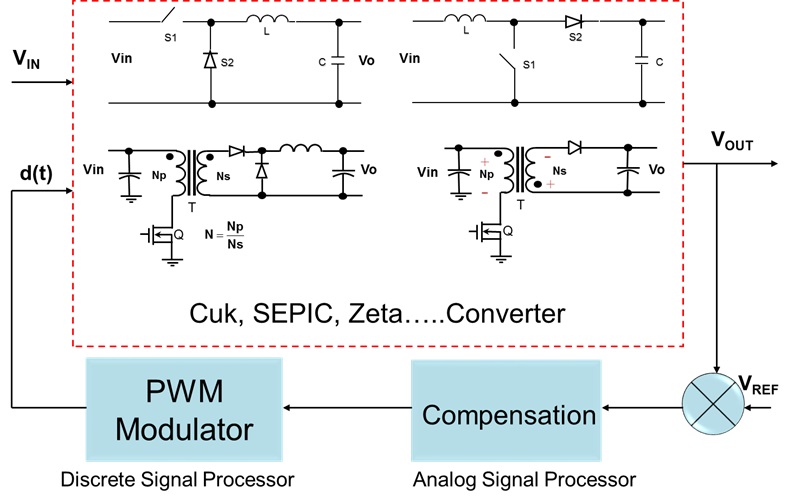

閉迴路概念方塊圖

迴授穩定的概念可套用在不同的電源架構,除了上圖四種架構外,還包含Linear Regulator也有迴授穩定的電路設計。以下列舉Voltage Control Mode介紹迴授控制。

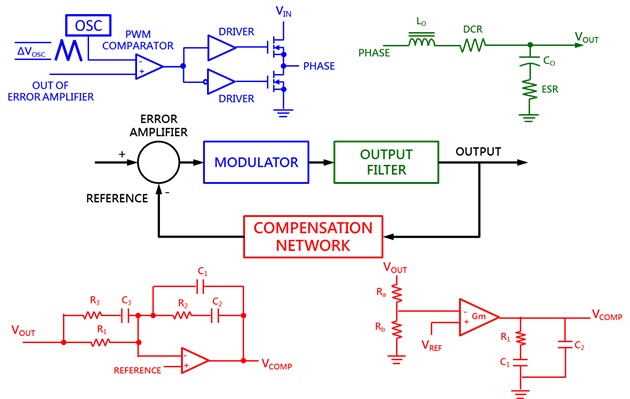

電壓控制模式閉迴路 (節錄於Intersil tb417 compensation application notes )

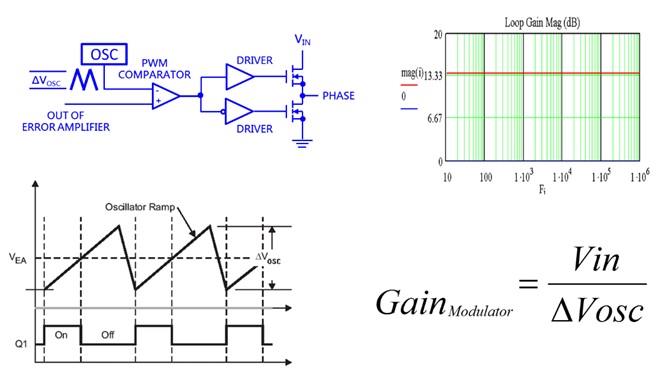

Modulator (節錄於Intersil tb417 compensation application notes )

注意輸入電壓設計改變會影響Bandwidth及Phase Margin。

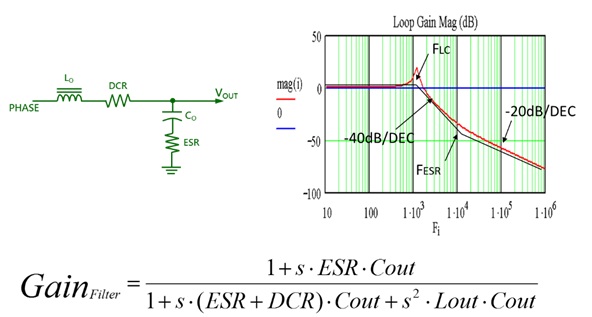

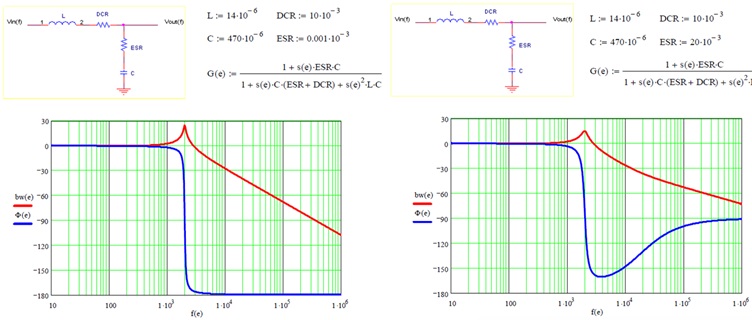

Output Filter (節錄於Intersil tb417 compensation application notes )

注意在電壓控制模式下,輸出電容與輸出電感會產生一個 Double Pole,使相位下降180°。另外選擇是當大的輸出電容等效串聯阻抗(ESR),可以在低頻產生一個Zero及使相位上升90°。當ESR太小,則Zero產生在高頻,對於穩定幫助不大。

輸出電容ESR貢獻

補償電路類別

Buck常見的補償線路為Type 2 & 3補償。另外在LDO有Feed-forward Compensation。

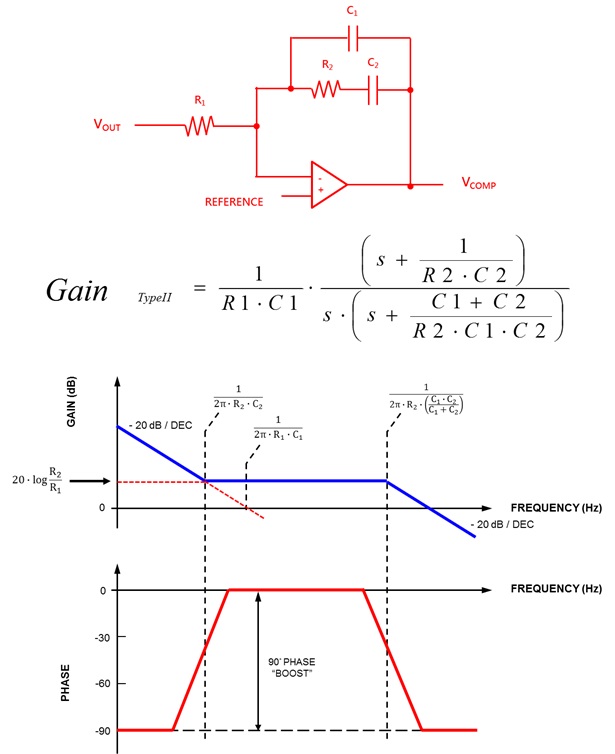

Type 2 Compensation

在低頻提供一個Zero,低頻Phase 上升90°,對於Phase Margin有幫忙。

在高頻提供一個Pole,高頻提供一個-20 dB斜率下降增益,可控制頻寬及抑制高頻雜訊增益。

Type 2 Compensation (節錄於Intersil tb417 compensation application notes )

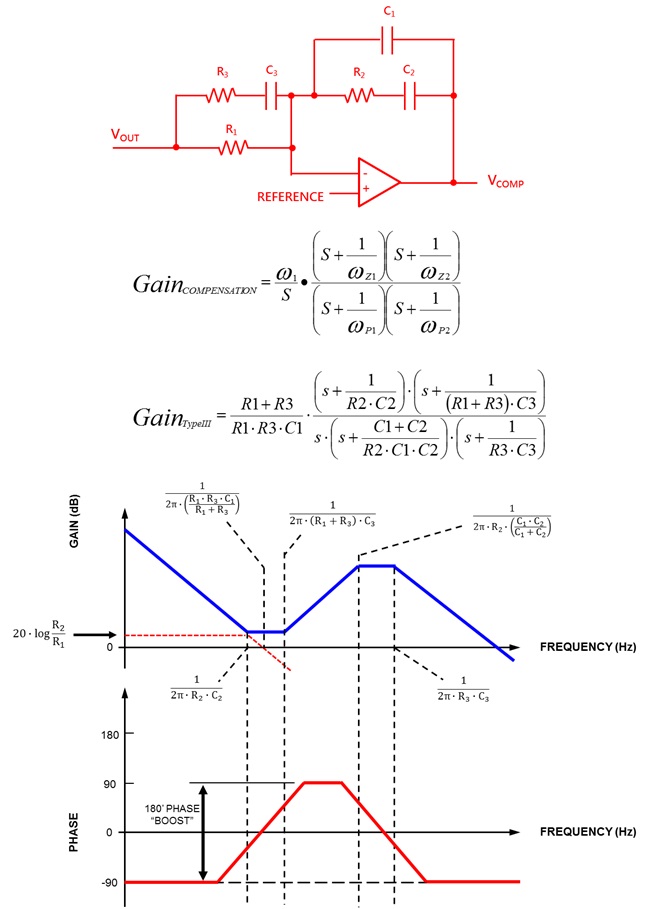

Type 3 Compensation

在低頻提供兩個Zero,低頻Phase 上升180°,對於Phase Margin有幫忙。

在高頻提供兩個Pole,高頻提供兩個-20dB斜率下降增益 (部分設計在同一頻率點,則成為一個Double Pole),可控制頻寬及抑制高頻雜訊增益。

Type 3 Compensation (節錄於Intersil tb417 compensation application notes )

補償電路設計順序

在進行補償電路之前,必須完成Buck其它的電路設計及選料。

- Buck IC決定了Control Mode

- VIN & Buck IC (△VOSC)決定了Modulation Gain

- LOUT & COUT決定了Double Pole頻率點 (FLC)

- 輸出電容ESR決定了輸出電容貢獻Zero頻率點 (FESR)

下列以Type 2介紹補償電路設計順序,零件位置可參考上面Type 2電路圖,詳細公式或者Type 3設計可參考Intersil tb417 compensation application notes

Step1:選擇2KΩ≦R1≦5KΩ

Step2:透過 R2/R1 設計Type2 Open Loop Gain,進而影響整個Closed Loop 期望BW。

Step3:選擇C2讓Type 2 Zero頻率,設計在輸出濾波器Double Pole頻率 (FZERO = FLC)

Step4:選擇C1讓Type 2 Pole頻率,設計在1/2 切換頻率 (FPOLE = 1/2 * FSW)

綜合Control Mode & Output Filter & ESR & Compensation的應用彙整表如下:

頻率補償彙整表

| Control Mode |

Output Filter LOUT & COUT |

輸出電容 ESR:大 補 Zero (Phase90⁰) 在低頻 → 有幫忙 |

輸出電容 ESR:小 補 Zero (Phase90⁰) 在高頻 → 沒幫忙 |

| Voltage Mode |

Double Pole 在低頻Phase掉180⁰ |

Type 2 Compensation 低頻 zero x 1 高頻 pole x 1 → 穩定 |

Type 3 Compensation 低頻 zero x 2 高頻 pole x 2 → 穩定 |

| Current Mode |

Single Pole 在低頻Phase掉90⁰ |

Type 2 Compensation 低頻 zero x 1 高頻 pole x 1 → 穩定 |

Type 2 Compensation 低頻 zero x 1 高頻 pole x 1 → 穩定 |

| COT Mode |

No Pole & Zero | 穩定 | VOUT,RIPPLE >Min Spec→ 振盪 VOUT,RIPPLE = IOUT,RIPPLE x ESR 輸出電容 ESR 不能過小 |

電路驗證

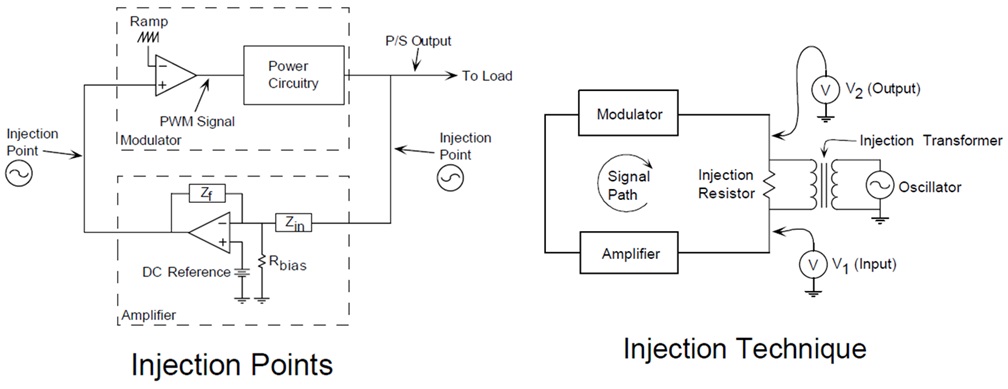

電路驗證品質是花錢買設備做風險管理,較正規的穩定驗證方法是透過波德圖量測「相位邊限、增益邊限、頻寬」去驗證電路的穩定及反應速度。

波德圖量測示意圖

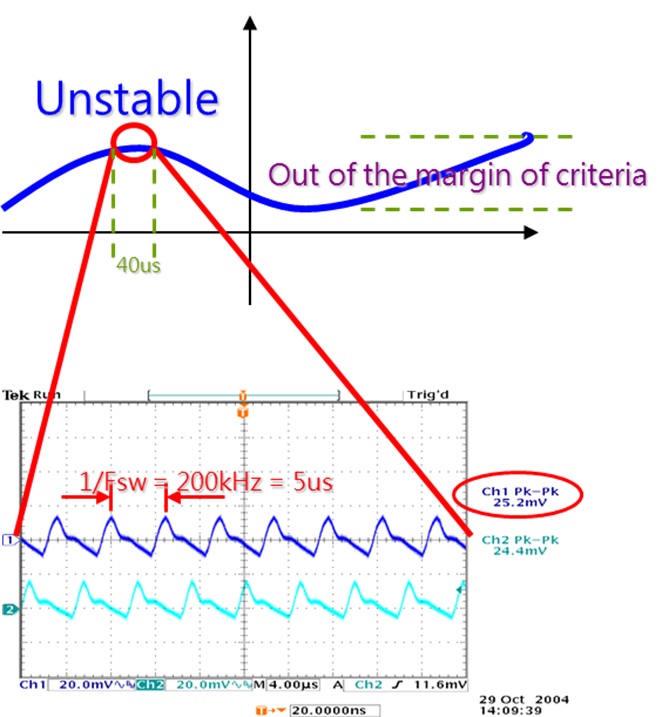

假設公司有採購設備經費困難,或者使用頻率不高,可透過好的策略供應商協助相關量測。而系統廠可在穩定負載下觀察Upper & Lower Side MOS的VG波形。在穩定的負載、輸入電壓、輸出電壓下應得到穩定的Duty,所以穩定的線路其VG波形的抖動 (Jitter) 應該要很小。或者可透過示波器觀察是否有低頻振盪。如下圖,輸出紋波電壓載在一個低頻振盪玄波上,此為不穩定振盪的迴授電路。

不穩定低頻振盪玄波