電路設計專欄 — Clock 研發管理 Part 1

【請點我參閱 石英振盪器課程影片】【請點我參閱 Clock 研發管理 Part 2】

時脈電路研發管理的順序:

HW Block (Clock Request) → Clock Tree (Clock Plan) → Part Selection (Xtal、OSC、Clock Buffer or Generator) → Schematic (DC Power Filter、Xtal、OSC or Clock IC ) → Pre-Sim (Parts IBIS) → Layout → Post-Sim (Layout Path + Parts IBIS) → SI & EMI Measurement

所以整體上要管理時脈電路研發含蓋「電路及零件動作原理、時脈零件技術、傳輸理論(Ex:PCB Impedance Control、Termination & Impedance Match)、訊號完整度(Signal Integrity, SI)、儀器概論及量測技巧、電磁干擾」等。最終如何在「訊號完整度、電磁干擾、成本交期」上找到平衡點。在此節路分享幾個學習重點。

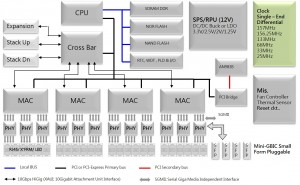

硬體方塊圖 (Hardware Block Diagram)

從硬體方塊圖中,可得知主Chip Set (Ex:CPU、MAC、PHY) 本身是否有振盪或者除頻線路,還有對於Input Clock Spec的需求。

網路交換機硬體方塊圖 (Networking Switch Block Diagram)

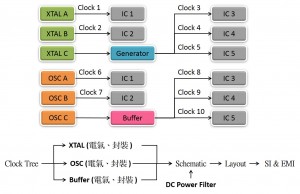

時脈樹狀圖 (Clock Tree)

由硬體方塊圖中可得知主IC本身的振盪條件,及對於Input Clock需求,去定義Clock Tree。這個的研發管理概念與Power Tree雷同。

時脈樹狀圖 (Clock Tree)

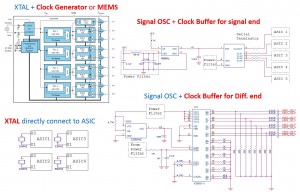

選料原則 (Parts Selection) → 線路設計 (Schematic Design) → 印刷電路板零件佈局走線 (Layout)

- 陶瓷諧振器 (Ceramic Resonator):當允許的誤差較寬,例如大於1000ppm。

- 石英晶體 (Crystal):主IC內部有振盪線路,且要求較高的Q值 (精準度),後續又可進階細分Metal Can、Resin、Glass、Seam Type不同的Package。

- 石英振盪器 (Oscillator):主IC內部沒有振盪線路,且該頻率只有單組需求,後續又可細分SPXO、PCXO、TCXO、VCXO、OCXO,另外還有不同邏輯準位的電壓及速度的區分。 目前也有許多使用MEMS (Micro Electro Mechanical Systems 微機電) 的技術去取代內含Crystal的OSC。

- 時脈緩衝器 (Clock Buffer):主IC內部沒有振盪線路,需要多組同頻率的需求,且對於訊號抖動參數要求較嚴苛,不可使用PLL (鎖相迴路)的線路。

- 時脈頻率產生器 (Clock Generator):主IC內部沒有振盪線路,需要多組相同或者不同的頻率的需求,且對於訊號抖動參數要求較鬆,可使用PLL (鎖相迴路)的線路。

以上選料也需要了解趨勢與主流規格。從不同的零件選擇組合,有各自對應的線路設計,除了XTAL 是純被動零件外,其他的零件都有主動IC。在此Clock屬於敏感線路,所以一般都會搭配直流電源濾波器 (DC Power Filter) 的線路,這是影響時脈電路PI、SI、EMI的源頭。在Layout則不外乎管理Return Path、 Image Plan、3W、Guard Traces…等。

時脈選擇方案 (Clock Solution)

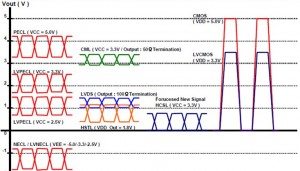

邏輯電壓準位 (Logic Level)

訊號完整度模擬 (SI Simulation)

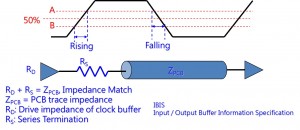

在Layout前稱為前期模擬 (Pre-Sim),在Layout之後稱為後期模擬 (Post-Sim),差別在於模擬是否包含 PCB Trace & Via 的衍生的參數。此時需要跟供應商要 IBIS Model。就以 Serial Termination 為範例觀察 Rising & Falling,若將RS擺放與Clock Output Pin在1/10的Rising時間的電子訊號長度內,則在RD與RS的不斷入射反射下,可以將RD與RS累加成一個電阻,所以只要RD+RS=ZPCB,則為阻抗匹配。模擬或者後續實際PCBA的實驗下,當加大RS則Rising / Falling斜率變緩,如果降低RS則Rising / Falling變陡,小到一定的程度就會有Overshoot & Undershoot的現象,可能會造成Amplitude。另外此處要學習PCB Trace Impedance與「PCB線寬、PP材的介電質、Trace與Image Plan、Micro Strip Line v.s. Strip Line」的關係。

訊號完整度模擬 (SI Simulation)