電路設計專欄 — Clock 研發管理 Part 2

【請點我參閱 石英振盪器課程影片】【請點我參閱 Clock 研發管理 Part 1】

訊號完整度及電磁干擾量測 (SI & EMI Measurement)

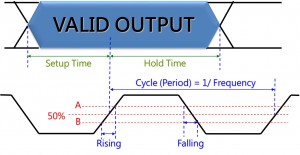

時脈 (Clock) 電路是整個電子產品的心臟,訊號的傳輸都依據時脈訊號的觸發 (Clock Trigger),Clock Trigger 務必在有效的資料 (Valid Output) 時間上,所以在訊號完整度會要求量測 Setup Time 及 Hold Time,換個角度看,必須要有穩定乾淨的 Clock 才有穩定的訊號傳輸品質。

Clock Trigger & Setup / Hold Time

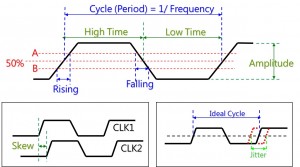

因此衍生了對 Clock SI 的要求,常見的參數包含「 Frequency ( = 1 / Period)、Duty ( = THigh / TPeriod)、Rising / Falling Time、Amplitude、Jitter、Skew 」。Jitter (抖動)及Skew是屬於較高端的量測,尤其 Jitter,是一般量測人員較容易混淆的量測技巧。

時脈參數(Clock Parameter)

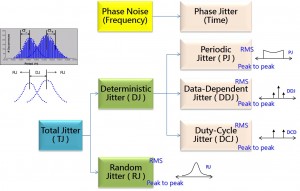

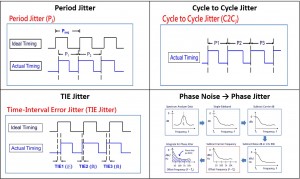

Jitter 因為含量及量測方法衍生出許多 Jitter 的專有名詞,所以首先需要了解各別 Jitter 的專有名詞定義,且依據 IC 的規格進行量測儀器的設定,進而量測 Jitter。

Jitter 含量成份

Jitter 量測方法分類

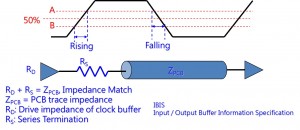

Rising / Falling Time的學習重點在於Clock IC Drive Impedance、Termination、PCB Impedance 的阻抗匹配。另外需以Rising / Falling規格去挑選示波器及探棒的類比頻寬,並非以頻率去挑選量測設備的頻寬,並且務必掌握示波器及探棒帶來的量測誤差。

Rising / Falling Time

在量測 Frequency 則須使用Clock Counter,會有較高的精準度,其餘量測 Duty、High/Low Time、Amplitude 難度不高,可透過 Scope Measurement 的挑選量測項目,即可得到波形及數值。一般 SI 與 EMI 為蹺蹺板的關係,例如當有極為陡峭的 Rising & Falling ,在SI來說是很好的表現,但因為高頻成分較多,可能 EMI 就不好。例如都 Jitter 小在 SI 是較好的表現,但在 EMI 的觀點來看,能量集中相對單點 Power 較大,此對 EMI 就不好。