電路設計專欄 — 功率電源電感剖析降壓式直流電路設計

「被動」零件,「主動」創造價值。

此處的「主動」包含了「電路理論」、「創新服務」兩個層面的含意。

「電路理論」:被動零件「功率電源電感」,扮演極重要的角色,左右周邊零件設計。

「創新服務」:以「功率電源電感」為核心,提供加值的服務。

此篇專欄將概略介紹「磁性元件分類、電路動作原理及重點參數、功率電源電感扮演角色、選料原則、零件互為替代性、零件匹配、Layout Guide」

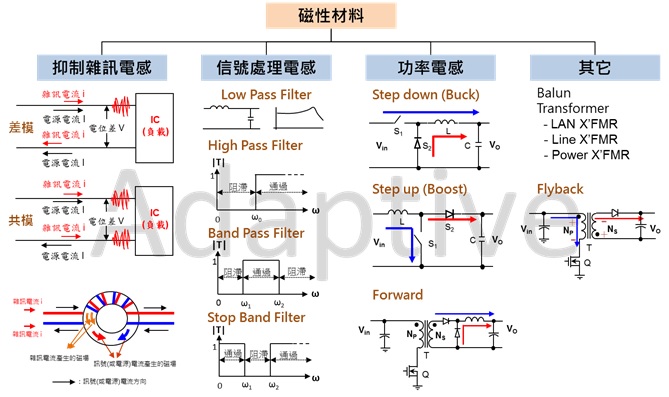

磁性元件分類:

如下圖,降壓式直流轉換的電源電感屬於功率電感,主要是儲能釋能角色。其電路功能類似Flyback(反馳式)的隔離式變壓器、Forward(順向式)的輸出電感。

電路動作原理:

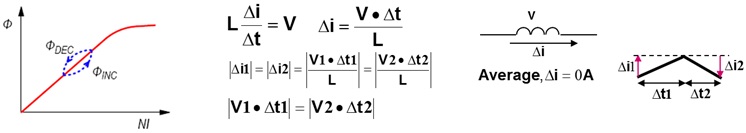

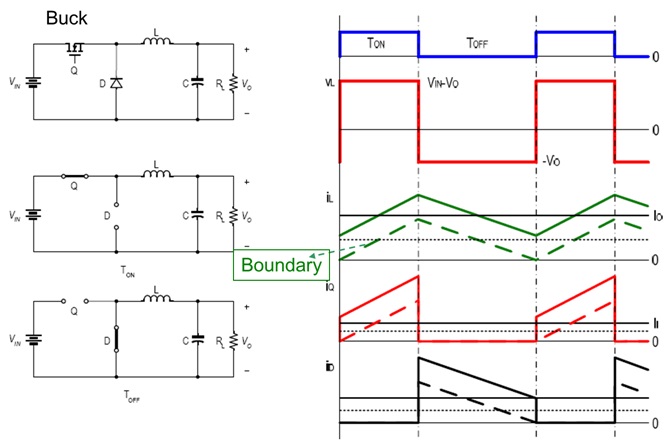

透過伏特-秒平衡(V-T Balance)概念,直流電源轉換IC控制功率晶體(Power MOS)開關,對於輸出電感儲能及釋能,且期望操作在連續導通模式(CCM:Continuous-Conduction Mode),此相對可得到較小的VOUT,RIPPLE(輸出紋波電壓)。

伏特-秒平衡(V-T Balance) 示意圖

降壓式直流電源轉換連續導通操作(CCM)模式示意圖

電路重點參數:

VOUT,RIPPLE (輸出紋波電壓)、VOUT,TRANSIENT (轉態輸出電壓)、Stable (穩定)、EMI (電磁干擾)、Efficiency (效率)、Thermal (熱)、Life & Reliability (壽命&可靠度)、Noise (噪音)、Cost (成本)、Lead Time (交期)。

在此只討論VOUT,RIPPLE (輸出紋波電壓)、VOUT,TRANSIENT (轉態輸出電壓)、Stable (穩定)、EMI (電磁干擾)、Efficiency (效率)、Thermal (熱),其餘內容可參考相關訓練課程。

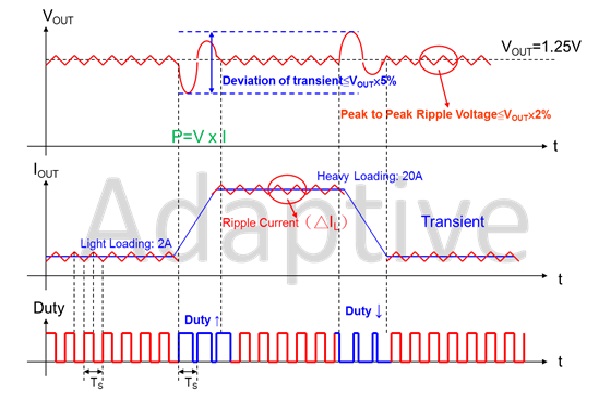

VOUT,RIPPLE、VOUT,TRANSIENT示意圖

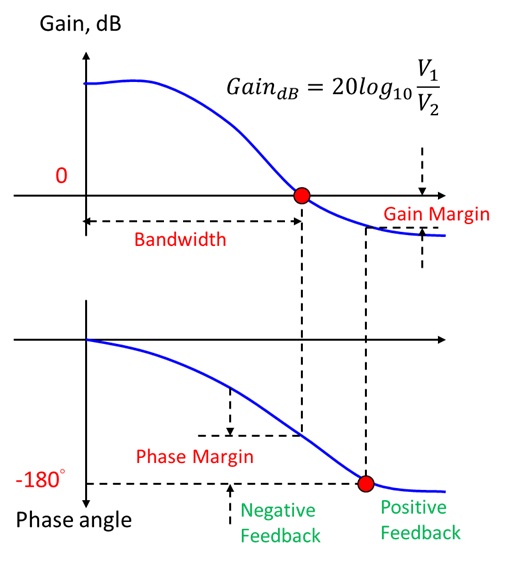

Stable:Phase Margin、Gain Margin、Bandwidth示意圖

一般電路設計參數規範:

- VOUT,RIPPLE (輸出紋波電壓) < 0.02 x VOUT

- VOUT,TRANSIENT (轉態輸出電壓):需參考IC設定負載轉態斜率。

- Stable (穩定):

- Phase Margin > 45°

- |Gain Margin| > 6dB

- Bandwidth:沒有硬性要求,越寬反應速度越快,但相對不穩定。

- EMI (電磁干擾):依客戶規範過 Class A or Class B,Under ? dB。

- Efficiency (效率):輕載、重載皆須符合產品規範。

- Thermal (熱):一般要求單體零件溫升<20°C,此除了影響壽命可靠度以外,另會影響精準度。

零件扮演角色:

- 降壓式電源轉換電路一般有「輸入電感」及「輸出電感」。「輸入電感」主要是將該組電源轉換電路與輸入電源做隔離,避免切換雜訊帶到共用輸入電源,另外可避免從Power帶出的傳導磁干擾。在實際電路會依據整組輸出負載大小及成本考量選擇是否擺放「輸入電感」。以下只項目討論「輸出電感」。

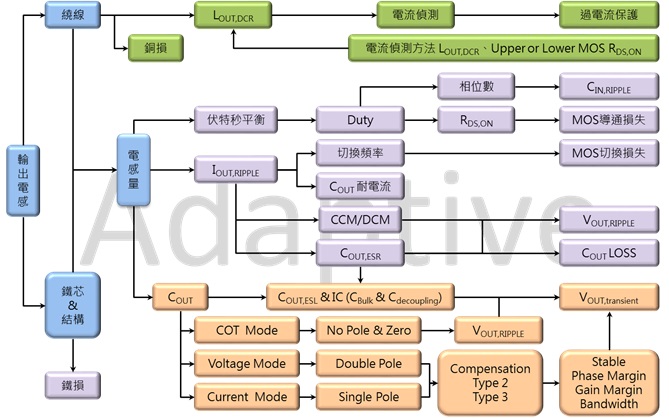

- 「輸出電感」主要功能包含「電流偵測、儲能釋能功率元件、遏制輸出紋波電流、與輸出電容組成輸出濾波器 (Output Filter)」。可依據下圖推敲「選料原則、零件互為替代性、零件匹配、Layout Guide、量測及解問題方法」

輸出電感與降壓式直流電源轉換設計關係圖

選料原則:

依下列影響,選擇對應電感及其它周邊零件參數,並且注意之間的匹配,以滿足電路規範。

1.) 繞線:「線徑截面積 (線粗細)」、「圈數(長度)」除了搭配「鐵芯(磁性材料、架構)」決定電感量以外,另外決定了直流電阻。影響層面如下:

- 電流偵測 (Current Sense):電流偵測常見方式包含「LOUT DCR、Upper MOS RDS,ON、Lower MOS RDS,ON、Current Sense Resistor」,當PWM IC看LOUT DCR時,則須注意LOUT DCR的誤差值。

- 銅損:P=I2R,線圈損失。

2.) 輸出電感儲能釋能:動作對應伏特-秒平衡 (V-T Balance),推導得Duty = VOUT/ VIN ,決定功率晶體切換導通時間)。許多零件計算跟Duty有關。

- 輸出電容耐電流:Duty 與 Phase Number (相位數,一般一個Phase 輸出電流上限約25A),及IOUT有關,可以推導輸入電容耐電流。

- 功率晶體導通損失:與Duty、IOUT與RDS,ON有關。

3.) 輸出電感遏制(Choke) IOUT,RIPPLE:電感量越大,則遏制IOUT,RIPPLE能力越強,所以相對IOUT,RIPPLE越小。而IOUT,RIPPLE對下列參數有影響。

- 功率晶體切換損失:與IOUT,RIPPLE、IOUT、FSW、開關上升下降時間等參數有關。

- 輸出電容耐電流:IOUT為直流負載,電容對直流視為開路,輸出電容只看到IOUT,RIPPLE。

- CCM / Boundary / DCM:一般設計期望在CCM (Continuous-Conduction Mode連續導通模式),電感儲能與釋能的電流是連續的,電感的能量不會釋放完,此IOUT,RIPPLE相對較小。此設計須考量IOUT輕載、與IOUT,RIPPLE。

- VOUT,RIPPLE 、COUT Loss:IOUT,RIPPLE 與 COUT ESR決定VOUT,RIPPLE 、COUT Loss。

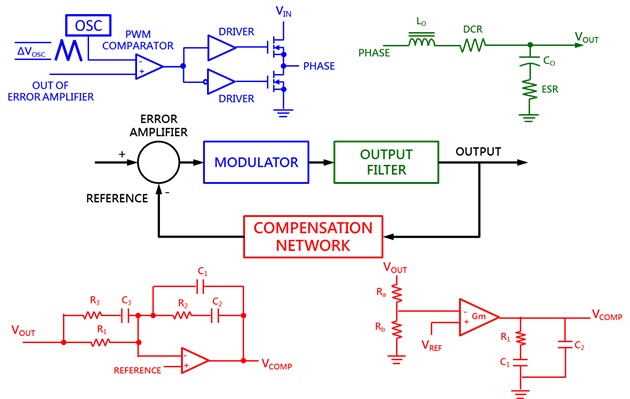

4.) 輸出濾波器:輸出電感與輸出電容在迴授電路上組成輸出濾波器。在不同的控制模式下,會有不同的設計考量。

- 電壓模式 (Voltage Mode):此輸出濾波器會造成Double Pole (極點),Phase會下降180°,在相對嚴苛條件下,需要有較好的補償(Compensation),例如Type 3。

- 電流模式 (Current Mode):此輸出濾波器只有Single Pole,Phase只會下降90°,所以補償可能只需要較簡單的Type 2即可。

- COT (Constant-On Time) mode:偵測VOUT,RIPPLE沒有Pole(極點) & Zero (零點)的概念。一般VOUT,RIPPLE有最小值限制,過小反而會造成誤動作。

- 輸出轉態電壓:當負迴授頻寬越寬、負迴授頻寬內的增益越大,越容易追隨輸出電壓變化,則輸出轉態電壓 (VOUT,TRANSIENT)越小。另外主IC旁的CBulk、CDecoupling、輸出電容量、輸出電容串聯等效電阻、輸出電容串聯等效電感…等,也會影響輸出轉態電壓。

電壓模式閉迴路迴授 (節錄於Intersil tb417 compensation application notes )

零件互為替代性:

- 鐵芯材料「Iron、Ferrite」之間替代關係

- 架構「Assembly、Molding」之間的替代關係

- 系統組裝「插件、貼片」之間的替代關係

- 磁路「封閉式、開放式」之間的替代關係

零件匹配:

- 輸入電感須注意與輸入電容之間的匹配性,以確保抑制輸入電壓的雜訊。

- 輸出電感須注意與輸出電容之間的匹配性,以確保同時滿足「VOUT,RIPPLE (輸出汶波電壓)、VOUT,TRANSIENT (轉態輸出電壓)、Stable (穩定)、EMI (電磁干擾)、Efficiency (效率)、Thermal (熱)、Life、Reliability (壽命可靠度)」。

Layout Guide:

- LIN & LOUT的主電流路徑都需要鋪銅,且零件擺放強調與Power MOS結構化。

- LOUT的DCR Current Sense,為敏感訊號,需要細線繞過主電流及驅動路徑。

- LOUT的Phase點有三種功能路徑。在主電流及Snubber路徑都強調鋪銅散熱,在Bootstrap路徑,則須獨立15 ~ 20mil粗線,強調與Upper MOS驅動路徑的結構化。

量測及解問題手法:

- LIN:觀察低頻透過Power Supply的傳導EMI及輸入電壓的雜訊。當輸入電壓的雜訊過大時,選擇是當輸入濾波器組合。當PWM IC FSW的基頻或者奇數頻EMI問題時,可修正Power MOS的驅動能力及確認Snubber。

- LOUT:量測VOUT,RIPPLE、VOUT,TRANSIENT、Stable (Phase Margin、Gain Margin、Bandwidth)、過電流保護(OCP)等。此有分成「時域」及「頻域」兩種量測,須注意時域示波器探棒的接地(Ground Bounce)。解問題概念可參考選料原則,至於詳細解問題方式及案例請參考相關訓練課程。

示波器探棒建議接地方式